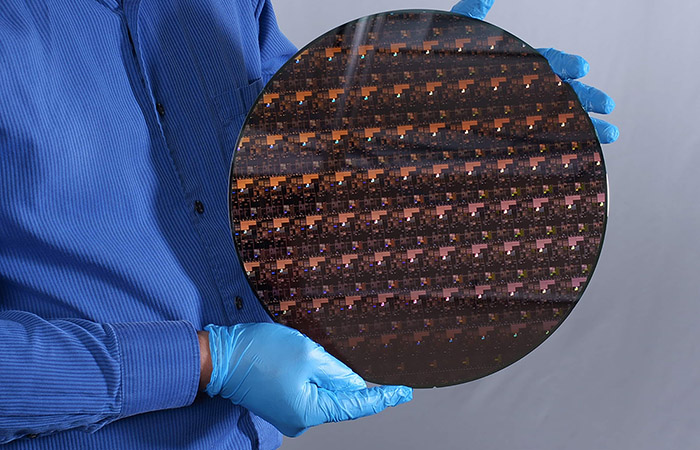

IBM이 트랜지스터 밀도 기준 2nm 공정으로 칩을 만들었다고 발표했습니다.

IBM이 트랜지스터 밀도 기준 2nm 공정으로 칩을 만들었다고 발표했습니다.

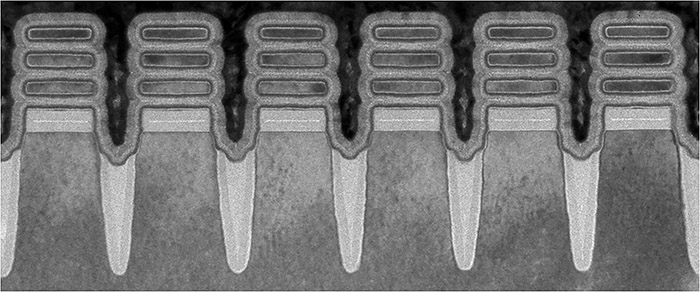

IBM이 선보인 2nm 칩은 각 트랜지스터가 3개의 적층된 수평 실리콘 시트로 구성되는 나노시트 방식을 적용했습니다.

이는 종전 핀펫 방식이 초미세 공정에서 누설 전류로 인한 간섭 등의 영향으로 한계를 보이면서 고려된 방식입니다.

나노시트는 삼성전자가 3nm 공정에서 적용할 예정으로 알려졌으나, IBM은 이를 2nm에서 구현했습니다.

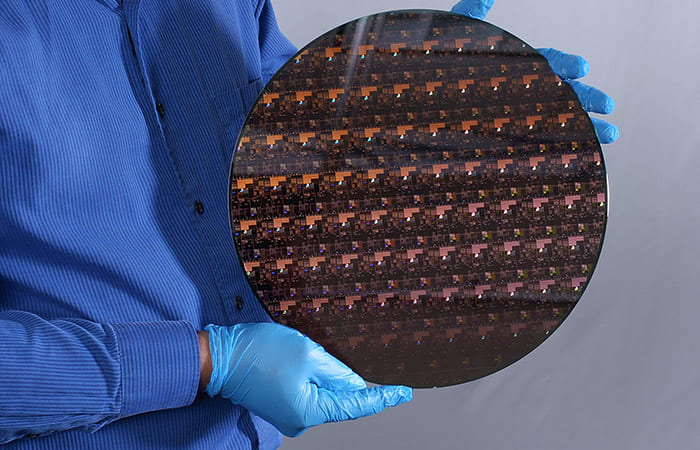

이번에 선보인 2nm 칩은 손톱 크기의 칩에 500억 개의 트랜지스터를 넣을 수 있는 것이라고 IBM 측은 밝혔습니다.

이번에 선보인 2nm 칩은 손톱 크기의 칩에 500억 개의 트랜지스터를 넣을 수 있는 것이라고 IBM 측은 밝혔습니다.

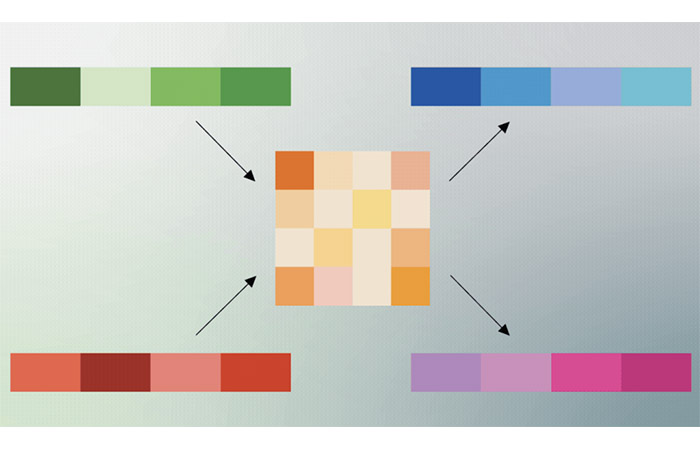

무엇보다 2nm 칩은 7nm 프로세서에 비해 동일 전력에서 45%, 동일 성능에서 75% 전력 소모를 감소시킬 수 있습니다.

하지만 IBM이 이번에 공개한 2nm 칩을 직접 양산하는 것은 아닙니다.

IBM은 기존 협력사인 삼성 뿐만 아니라 최근 파트너십을 맺은 인텔과 기술 적용을 논의할 것으로 보입니다.